Invariavelmente isto vai acabar por aparecer, por isso, mais um tópico, para mais uma ISA para CPU.

Para quem se quiser inteirar

https://riscv.org/about/

Para quem se quiser inteirar

https://riscv.org/about/

https://www.cnx-software.com/2020/1...nner-risc-v-processor-to-power-12-linux-sbcs/As far as I understand companies are still under NDA with Allwinner, so they can divulge too much. But here’s what the $12.5 Sipeed Linux RISC-V board specifications should look like based on public information available at this stage:

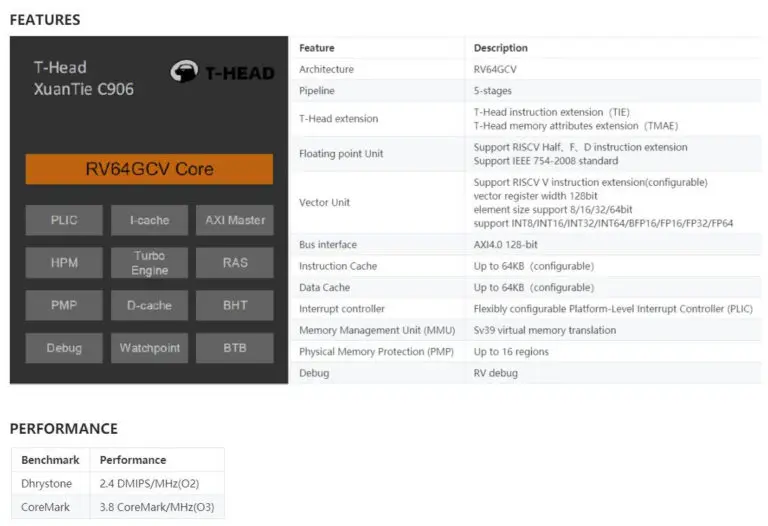

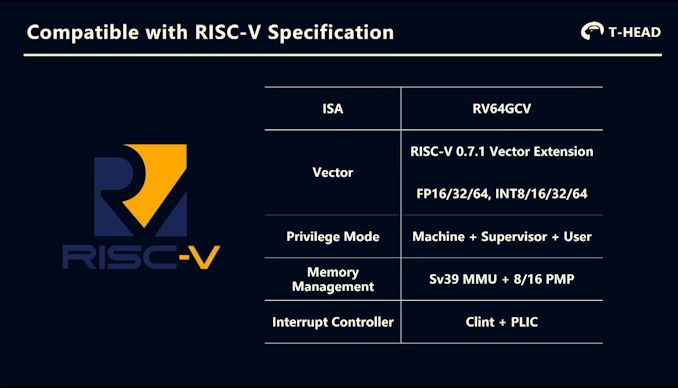

- SoC – Unnamed Allwinner single-core XuanTie C906 64-bit RISC-V (RV64GCV) processor @ up to 1 GHz; 22nm manufacturing process

- GPU – 2D accelerator only (similar to what is found in Allwinner V3s)

- VPU – H.265/H.264

- System Memory – 64MB to 256MB DDR3 (PoP); external memory version may also be available

- Storage – MicroSD card socket

- Video Output / Display I/F – HDMI, RGB LCD

- Camera I/F – DVP and MIPI CSI

- Networking – GMAC (Gigabit Ethernet MAC), optional WiFi and Bluetooth module

- USB – USB host and OTG

mas Single Core e sem 3D

mas Single Core e sem 3D

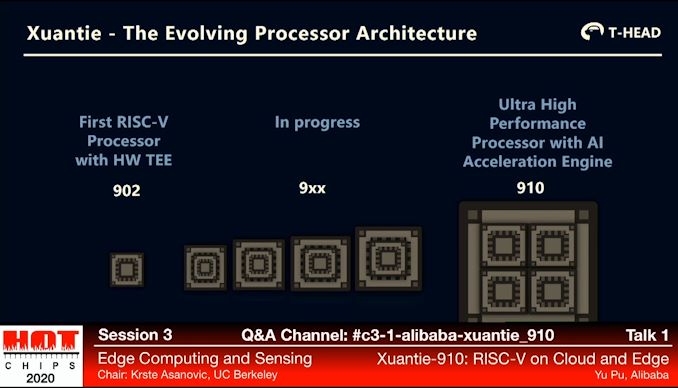

06:10PM EDT - Xuantie-902 (M0+ like) with hardware TEE up to Xuantie-910

06:10PM EDT - 903, 907,908 coming

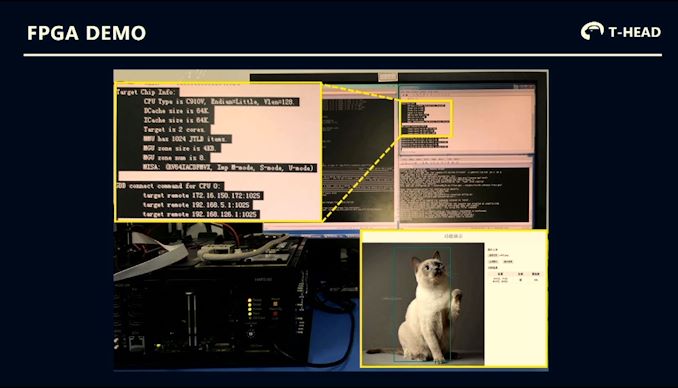

06:25PM EDT - Here's an AI workload on an FPGA simulation of X910

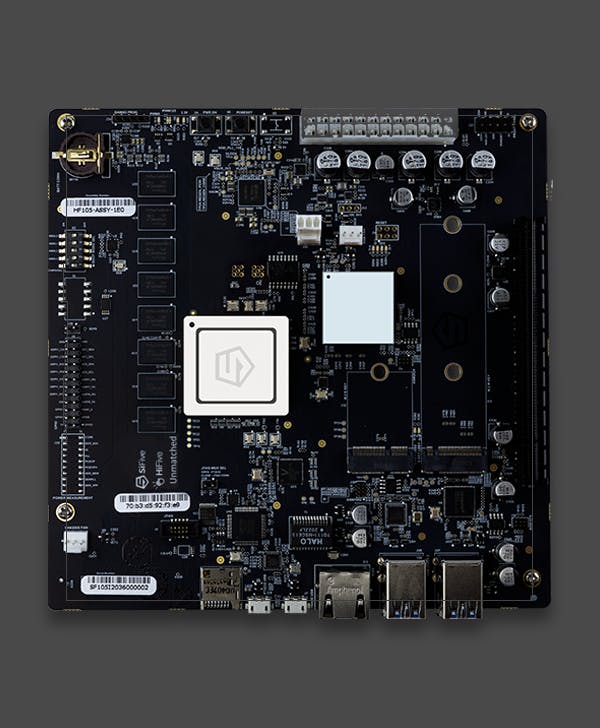

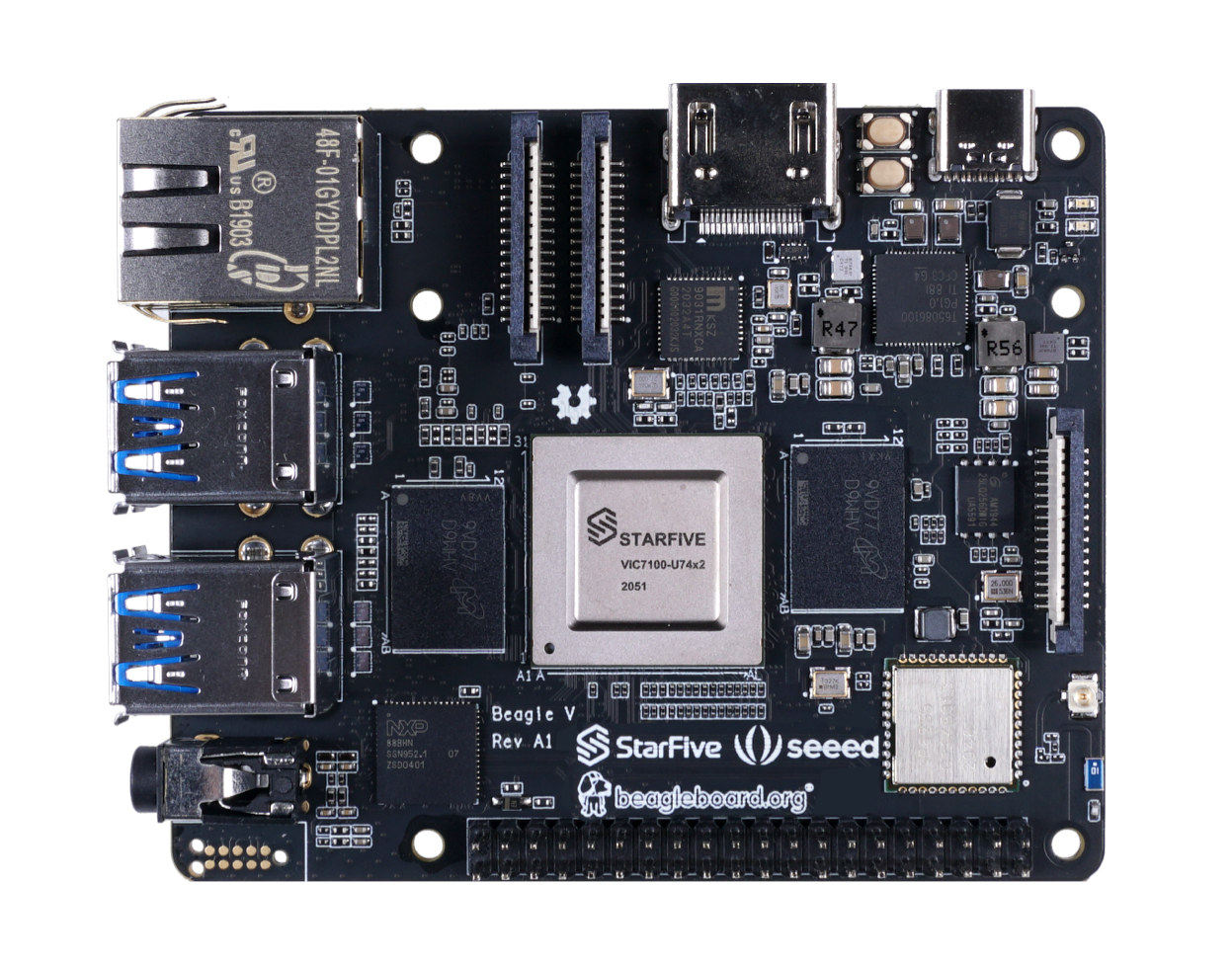

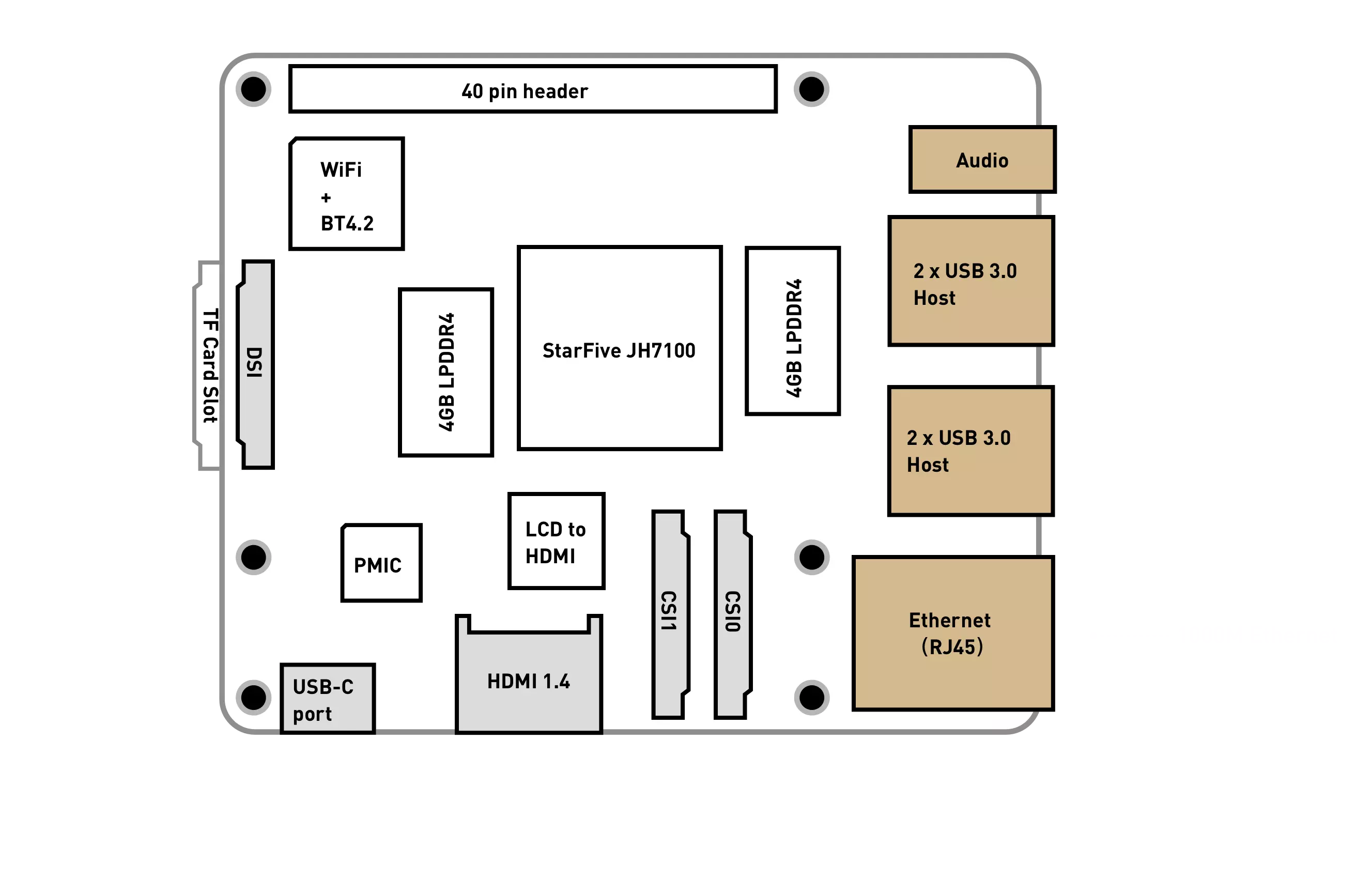

Et tu BBC

BeagleBoard.org foundation, Seeed Studio, and Chinese fabless silicon vendor Starfive partnered to design and launch the BeagleV SBC (pronounced Beagle Five) powered by StarFive JH7100 dual-core SiFive U74 RISC-V processor with Vision DSP, NVDLA engine, and neural network engine for AI acceleration.

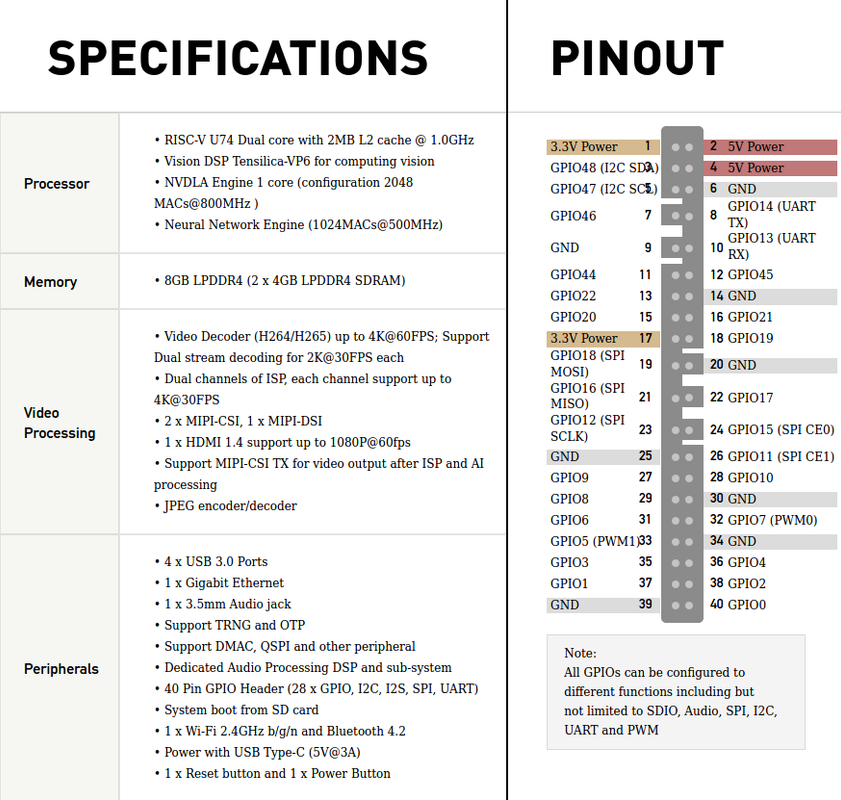

BeagleV specifications:

- SoC – StarFive JH7100 Vision SoC with:

- RISC-V U74 dual-core with 2MB L2 cache @ 1.5 GHz

- Vision DSP Tensilica-VP6 for computing vision

- NVDLA Engine 1 core (configuration 2048 MACs @ 800MHz – 3.5 TOPS)

- Neural Network Engine (1024MACs @ 500MHz – 1 TOPS)

- VPU – H.264/H.265 decoder up to 4Kp60, dual-stream decoding up to 2Kp30

- JPEG encoder/decoder

- Audio Processing DSP and sub-system

- System Memory – 4GB or 8GB LPDDR4

- Storage – MicroSD card slot

- Video output

- 1x HDMI port up to 1080p30

- 1x MIPI DSI interface up to 4Kp30

- MIPI-CSI TX for video output after ISP and AI processing

- Camera

- Dual channels of ISP, each channel support up to 4K @ 30FPS

- 2 x MIPI-CSI Rx

- Audio – 3.5mm audio jack

- Connectivity – 1x Gigabit Ethernet, 2.4 GHz 802.11b/g/n WiFi 4, and Bluetooth 4.2

- USB – 4x USB 3.0 Ports

- Expansion – 40-pin GPIO header with 28 x GPIO, I2C, I2S, SPI, UART

- Security – Support TRNG and OTP

- Misc – Reset and power buttons

- Power Supply – 5V/3A via USB Type-C port

https://www.cnx-software.com/2021/0...are-risc-v-linux-sbc-targets-ai-applications/One obvious item missing from the specifications is a GPU, and I was told while the first batch scheduled in March will be GPU less, but the next batch – slated to be manufactured in September – will come with an Imagination Technologies GPU.

https://www.phoronix.com/scan.php?page=news_item&px=Imagination-New-Open-Graphics"We need you to join the Linux driver development team and put your software development skills to the test. You will focus on developing a new Linux open source graphics driver stack, including Mesa and kernel-mode drivers. You will be a member of a small team, working alongside other software teams implementing the existing driver stack for PowerVR graphics hardware."

Imagination’s PowerVR GPU Driver (DDK v1.13 release onwards) supports RISC-V as a target application processor and will be easily integrated with the PicoRio single-board computer platform. Imagination is also creating a new open-source GPU driver to provide a complete, up-streamed open-source kernel and user-mode driver stack to support Vulkan® and OpenGL® ES within the Mesa framework.

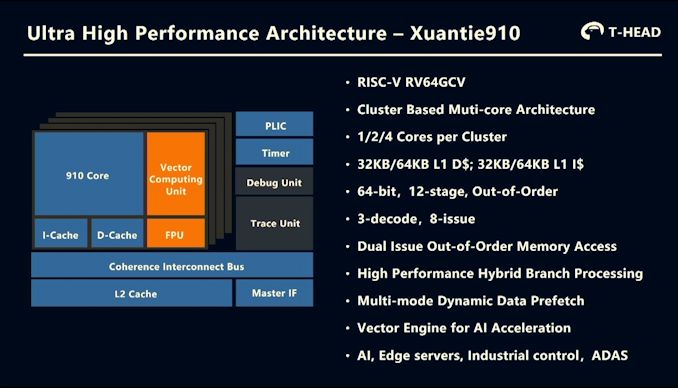

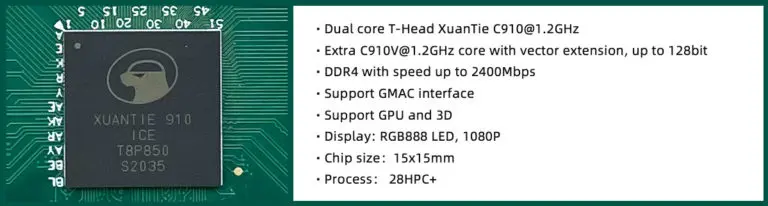

The demo above runs on ICE EVB powered by a XuanTie C910 based high-performance SoC board developed by T-Head. Specifically, the ICE SoC integrates two XuanTie C910 cores (RV64) @ 1.2 GHz, one other XuanTie C910V core @ 1.2 GHz with vector extensions, a single-core 3D GPU core [Update: it’s a Vivante GC8000UL GPU], DDR4 memory support, a GMAC (Gigabit Ethernet) interface, as well as 4Kp60 HEVC/AVC/JPEG video decoding. The display resolution appears limited to 1920×1080 however.

A group of enthusiasts are proposing a new set of graphics instructions designed for 3D graphics and media processing. These new instructions are built on the RISC-V base vector instruction set. They will add support for new data types that are graphics specific as layered extensions in the spirit of the core RISC-V instruction set architecture (ISA). Vectors, transcendental math, pixel, and textures and Z/Frame buffer operations are supported. It can be a fused CPU-GPU ISA. The group is calling it the RV64X as instructions will be 64-bit long (32 bits will not be enough to support a robust ISA).

The team says their motivation and goals are driven by the desire to create a small, area-efficient design with custom programmability and extensibility. It should offer low-cost IP ownership and development, and not compete with commercial offerings. It can be implemented in FPGA and ASIC targets and will be free and open source. The initial design will be targeted to low-power microcontrollers. It will be Khronos Vulkan-compliant, and over time support other APIs (OpenGL, DirectX and others).

RV64X block diagramThe final hardware will be a RISC-V core with a GPU functional unit. To the programmer it will look like a single piece of hardware with 64-bit long instructions coded as scalar instructions. The programming model is an apparent SIMD, that is, the compiler generates SIMD from prefixed scalar opcodes. It will include variable-issue, predicated SIMD backend, vector front-end, precise exceptions, branch shadowing and much more. There won’t be any need for RPC/IPC calling mechanism to send 3D API calls to/from unused CPU memory space to GPU memory space and vice-versa, says the team. And it will be available as 16-bit fixed point (ideal for FPGAs), as well as 32-bit floating point (ASICs or FPGAs).

The design will employ the Vblock format (from the Libre GPU effort):

- It is a bit-like VLIW (only not really)

- A block of instructions is pre-fixed with register tags which give extra context to scalar instructions within the block

- Sub-blocks include: vector length, swizzling, vector/width overrides and predication.

- All this is added to scalar opcodes

- There are no vector opcodes (and no need for any)

- In the vector context, it goes like this: if a register is used by a scalar opcode, and the register is listed in the vector context, vector mode is activated

- Activation results in a hardware-level for-loop issuing multiple contiguous scalar operations (instead of just one).

- Implementers are free to implement the loop in any fashion they desire: SIMD, multi-issue, single-execution.

RV64X’s scalable designThe RV64X reference implementation will include:

- Instruction/Data SRAM Cache (32KB)

- Microcode SRAM(8KB)

- Dual Function Instruction Decoder

- Hardwired implementing RV32V and X

- Micro-coded Instruction Decoder for custom ISA

- Quad Vector ALU (32 bits/ALU—fixed/float)

- 136-bit Register Files (1K elements)

- Special Function Unit

- Texture Unit

- Configurable local Frame Buffer

https://www.eenewseurope.com/news/picocom-tapes-out-multicore-risc-v-openran-chip-oranic-boardThe PC802 chip combines 32 RISC-V cores and 3 CEVA vector processor cores with 25Mbits of SRAM. One chip can be used as the controller for 4G or 5G small cell, but four can also be used on a card to manage 16 remote radios from different suppliers. Two cards can handle 32 radio heads.

“The chip itself is on the point of tapeout for engineering lots on TSMC 12nm,” said Peter Claydon, president of PicoCom in Bristol.

The test chip, shown in figure 1 below, contains four vector processing micro-tiles (VPU) composed of an Avispado RISC-V core designed by SemiDynamics and a vector processing unit designed by Barcelona Supercomputing Center and the University of Zagreb. Each tile also contains a Home Node and L2 cache, designed respectively by Chalmers and FORTH, that provide a coherent view of the memory subsystem. The Stencil and Tensor accelerator (STX) was designed by Fraunhofer IIS, ITWM and ETH Zürich, and the variable precision processor (VRP) by CEA LIST. These specialized accelerators are connected with very high-speed network on chip and SERDES technology from EXTOLL.

https://www.hpcwire.com/off-the-wir...announces-epac1-0-risc-v-test-chip-taped-out/The EPAC design was finalized by Fraunhofer IIS for chip integration in GLOBALFOUNDRIES 22FDX low-power technology and will be integrated and evaluated in the FPGA-based board designed by FORTH, E4 and the University of Zagreb. The successful fabrication of EPAC will showcase the next step in accelerator-based green HPC computing.

https://www.bloomberg.com/news/arti...ifive-is-said-to-draw-intel-takeover-interestChipmaker SiFive Is Said to Draw Intel Takeover Interest

SiFive Inc., a startup that designs semiconductors, has received takeover interest from investor Intel Corp., according to people familiar with the matter.

- Intel offered to acquire SiFive for more than $2 billion

- Talks are early and SiFive could chose to remain independent

Intel offered to acquire SiFive for more than $2 billion, one of the people said, asking not to be identified because the matter is private.

The San Mateo, California-based company has been in talks with potential advisers on how to handle the takeover interest, the people added.

The company has received takeover offers from multiple parties other than Intel, one of the people said. It has also fielded offers for an investment, which could be a preferable route, the person added.

Discussions are early, there’s no guarantee any deal will be reached, and SiFive may choose to remain independent.

SiFive was last valued at around $500 million when it raised funds in 2020, according to data provider PitchBook.

A representative for Intel declined to comment. A representative for SiFive didn’t respond to requests for comment.

ARM Rival

SiFive is a designer of chips that are based on the RISC-V architecture, an attempt to bring open-source standards to semiconductor design making it cheaper and accessible to customers.

Interest in SiFive has increased since Nvidia Corp. agreed in September to pay $40 billion for SoftBank Group Corp.’s Arm Ltd., which like SiFive, licenses chip and process designs.

SiFive Chief Executive Officer Patrick Little is a chip industry veteran. He joined SiFive last year from Qualcomm Inc. where he was a senior vice president in charge of their automotive business.

Read More: Silicon Valley’s Next Revolution Is Open Source Semiconductors

SiFive is seen as a potential beneficiary if Nvidia’s deal goes through because Arm’s customers are concerned the company might work less collaboratively with them, the people said.

The company’s investors include SK Hynix Inc., Spark Capital and Prosperity7 Ventures, the venture arm of Saudi Arabia’s state-owned energy producer Aramco. It also is backed by the venture arms of chipmaker Qualcomm and of hardware maker Western Digital Corp. It last raised $61 million in a funding round in 2020.